# 15 V, 8 A, HIGH PERFORMANCE HALF BRIDGE

#### **Features**

- ZqFET™ High Performance Technology

- Supports Switching Frequencies up to 2 MHz

- $R_{DS(ON)4.5V}$  of 20 / 8 m $\Omega$  (Q1 / Q2)

- Extremely Low Gate Charge and Output Capacitance for Low Switching Losses

- QFN 3.7 mm x 4 mm Thermally Enhanced Package

## **Applications**

- Small. Efficient DC/DC Converters

- Battery Powered Electronics

- Power Blocks for Buck or Buck-Boost Converters

## **Product Description**

The SZPB9317A-B is a compact, high efficiency half bridge optimized for high frequency applications. It contains Silanna's proprietary  $ZqFET^{TM}$  in a half bridge configuration, capable of delivering 8 A of output current with a wide range of inputs up to 15 V.

Silanna's proprietary *ZqFET*<sup>TM</sup> technology offers industry's benchmark performance that reduces both switching and conduction losses for operation at switching frequencies up to 2 MHz.

The SZPB9317A-B has been optimally designed for operation as a half bridge for high frequency DC/DC buck converters. The device is fabricated in a standard silicon process. The  $ZqFET^{TM}$  structure provides for extremely low, world class switching losses for a given on resistance rivalling devices fabricated in exotic processes.

The SZPB9317A-B is available in a space-saving and thermally enhanced QFN 3.7 mm x 4 mm package.

#### **Device Overview**

**WARNING**: These devices have limited built-in ESD protection. The leads should be shorted together with the device placed in conductive containers during storage or handling to prevent electrostatic damage to the Power ZqFET®'s MOS gates.

SZPB9317A-B

## DATASHEET

**Contents**

| Features                           | 1  |

|------------------------------------|----|

| Applications                       | 1  |

| Product Description                | 1  |

| Pin Descriptions                   | 3  |

| Pin Definitions                    | 3  |

| Internal Block Diagram             | 4  |

| Absolute Maximum Ratings           | 4  |

| Thermal Information                | 5  |

| Recommended Operating Conditions   | 5  |

| Static Electrical Characteristics  | 6  |

| Dynamic Electrical Characteristics | 7  |

| Product Ordering Information       | 8  |

| Product Image                      | 8  |

| Package Dimensions                 | 9  |

| Recommended PCB Footprint          | 10 |

| Revision History                   | 11 |

# **Figures**

| rigure it rop transparent view        | ت د      |

|---------------------------------------|----------|

| Figure 2: Internal Block Diagram      | 4        |

| Figure 3: SZPB9317A-B Product Image   | 8        |

| Figure 4: F34 Package Dimensions      | <u>C</u> |

| Figure 5: Recommended PCB Footprint . | 10       |

# **Pin Descriptions**

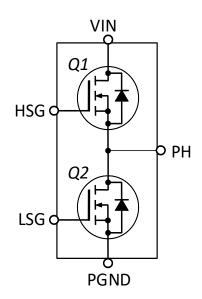

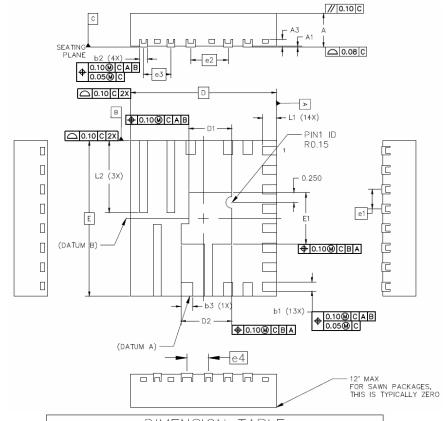

**Figure 1: Top Transparent View**

### **Pin Definitions**

| Pin#  | Name | Description                                                                                              |

|-------|------|----------------------------------------------------------------------------------------------------------|

| 1-10  | NC   | No connect. May be used to connect to a large PCB pad area of VIN.                                       |

| 11    | VIN  | Input voltage to Power Block, drain of Q1.                                                               |

| 12    | LSG  | Input connection to the gate of the low-side FET, Q2.                                                    |

| 13    | PGND | Power ground connection to the source of the low-side FET, Q2.                                           |

| 14-15 | PH   | Connections to the phase node of the half bridge, drain of low-side FET and source of the high-side FET. |

| 16    | HSG  | Input connection to the gate of the high-side FET, Q1.                                                   |

| 17-18 | NC   | No connect. May be used to connect to a large PCB pad area of VIN.                                       |

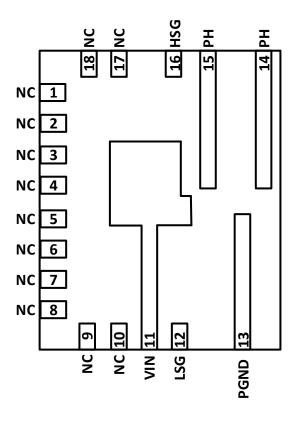

# **Internal Block Diagram**

Figure 2: Internal Block Diagram

## **Absolute Maximum Ratings Note 1**

(Ta = 25°C Unless Otherwise Specified, relative to PGND.)

| Parameter                       | Symbol    | Device | Value    | Units |

|---------------------------------|-----------|--------|----------|-------|

| Gate-Source Voltage             | Vac       | Q1     | 9.0      | V     |

| Gale-Source voltage             | Vgs       | Q2     | 9.0      | V     |

| VIN Voltage                     | Vvin      |        | 18.0     | V     |

| PH Voltage, DC                  | Vphase_dc |        | 18.0     | V     |

| PH Voltage, AC (<10 ns)         | Vphase_ac |        | 25.0     | V     |

| DC Drain-Source Current         | Id        | Q1     | 8        | ^     |

| (Tj = 150 °C)                   | ld        | Q2     | 13       | Α     |

| Pulsed Drain-Source Current (2) | ldm       | Q1     | 12       |       |

| Pulsed Drain-Source Current     | ldm       | Q2     | 20       | Α     |

| Operating Junction Temperature  | Tj        | вотн   | -40/+150 | °C    |

| Storage Temperature             | Ts        | BOTH   | -50/+150 | °C    |

- 1) These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to conditions greater than Recommended Operating Conditions will affect device reliability.

- 2) Pulse width ≤ 1ms, duty cycle ≤ 2%.

## Thermal Information Note 1

| Parameter                                              | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Тур. |      | Units |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|

| Thermal Resistance Junction to Ambient                 | R <sub>OJA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q1   | 30.1 |       |

| Thermal Resistance Junction to Ambient                 | Көја                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q2   | 31.7 |       |

| Thermal Peciatones, Junction to Ton of Backage         | unation to Tan of Dankage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 14.7 |       |

| Thermal Resistance Junction to Top of Package          | $R_{\Theta JC(TOP)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q2   | 15.9 |       |

| Thermal Decistores Investigate Decard                  | Desire to Desire |      | 6.6  | °C/W  |

| Thermal Resistance Junction to Board                   | Rejb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q2   | 8.3  |       |

| Thermal Characterization Parameter - Junction to top   | Ψл                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.8  |      |       |

| Thermal Characterization Parameter - Junction to board | $\Psi_{JB}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 8.1  |       |

#### Notes:

1) Simulated on 2S2P board based upon JESD51-5 specifications.

## **Recommended Operating Conditions**

(Ta = 25°C Unless Otherwise Specified.)

| Parameter                      | Symbol           | Conditions                                                                          | Max.     | Units |

|--------------------------------|------------------|-------------------------------------------------------------------------------------|----------|-------|

| VIN Operating Voltage (1)      | V <sub>VIN</sub> | Insure any ringing on PH pins does not exceed Absolute Maximum ratings for PH pins. | 15       | V     |

| Gate-Source Operating Voltage  | V <sub>G</sub> s | -                                                                                   | 5.5      | V     |

| Operating Frequency (2)        | Fsw              |                                                                                     | 2        | MHz   |

| Operating Junction Temperature | TJ               |                                                                                     | -40/+125 | °C    |

- 1) Attention to proper VIN supply bypassing and tight PCB layout must be observed to keep the peak voltage of any ringing on the phase node, at the PH pins, below the Absolute Maximum Ratings above.

- 2) The device is very capable of switching at higher frequencies. Contact Silanna with your requirements so we can best ensure the highest reliability for the device in your applications at higher switching frequencies.

# **Static Electrical Characteristics**

(Ta= 25°C Unless Otherwise Specified)

| Parameter                   | Symbol                  | Conditions                        |    | Min. | Тур. | Max. | Units       |

|-----------------------------|-------------------------|-----------------------------------|----|------|------|------|-------------|

| Cata Sauraa Laakaga Currant | Loren                   | Vds = 0 V, Vgs = +5.5 V           |    |      | 10   | 100  | <b>~</b> Λ  |

| Gate-Source Leakage Current | Igss                    | Vds = 0 V, Vgs = -5.5             | V  | -100 | -10  |      | nA          |

| Gate-Source Threshold       | Vth                     | Vgs = Vds, Id = 250 μA            | Q1 | 0.9  | 1.0  | 1.2  | V           |

| Voltage (ext)               | VUI                     | νg3 = να3, ια = 200 μ/λ           | Q2 | 0.75 | 1.0  | 1.2  | V           |

| Drain-Source Breakdown      | Bvdss                   | C                                 |    | 25   |      |      | V           |

| Voltage                     | Dvuss                   | Bvdss $Vgs = 0 V, Id = 250 \mu A$ | Q2 | 25   |      |      | \ \ \ \ \ \ |

| Drain-Source Leakage        | Idoo                    | VDS = 12.5 V, VGS=0               | Q1 |      | 70   | 1000 | Λ           |

| Current                     | ldss                    | VDS = 12.5 V, VGS=0               | Q2 |      | 120  | 2000 | nA          |

| Drain-Source On-State       | R <sub>DS(ON)4.5V</sub> | Vgs = 4.5 V, Id = 8 A             | Q1 |      | 20   | 27   | mO.         |

| Resistance (4.5 V)          |                         |                                   | Q2 |      | 8.5  | 11   | mΩ          |

| Pody Diodo Forward Voltage  | V <sub>SD</sub>         | Vgs = 0 V, ld = 1 A               | Q1 |      | 0.72 |      | V           |

| Body Diode Forward Voltage  |                         |                                   | Q2 |      | 0.69 |      | V           |

- 1) Measured using pulse techniques pulse width = 300 µs and duty cycle = 1% to minimize junction self-heating.

- 2) Measured using 4-wire (Kelvin) voltage sensing within 0.05" (2 mm) of the drain and source aggregate connections.

# **Dynamic Electrical Characteristics**

(Ta= 25°C Unless Otherwise Specified)

| Parameter                       | Symbol  | Conditions               |    | Min. | Тур. | Max. | Units  |  |

|---------------------------------|---------|--------------------------|----|------|------|------|--------|--|

| Cata Saurea Innut Canasitanas   | Cina    | Vds = 12.5 V, Vgs = 0 V, | Q1 |      | 240  | 310  | ~ F    |  |

| Gate-Source Input Capacitance   | Ciss    | f = 1.0 MHz              | Q2 |      | 560  | 630  | pF     |  |

| Drain-Source Output             | Coss    | Vds = 12.5 V, Vgs = 0 V, | Q1 |      | 210  | 280  | nE     |  |

| Capacitance                     | CUSS    | f = 1.0 MHz              | Q2 |      | 500  | 600  | pF     |  |

| Reverse Transfer (Drain-Gate)   | Crss    | Vds = 12.5 V, Vgs = 0 V, | Q1 |      | 5.5  |      | ۲<br>ا |  |

| Capacitance                     | CISS    | f = 1.0 MHz              | Q2 |      | 13.0 |      | pF     |  |

| Cata Pagiatanas                 | Da      |                          | Q1 |      | 0.3  |      | Ω      |  |

| Gate Resistance                 | Rg      | Rg                       | Q2 |      | 0.5  |      |        |  |

| Total Cata Charge (Vac – 4 5 V) | Qg(4.5) | Vds = 12.5 V, Ids = 8 A  | Q1 |      | 1.6  | 1.9  | nC     |  |

| Total Gate Charge (Vgs = 4.5 V) |         | Vds = 12.5 V, Ids = 13 A | Q2 |      | 3.9  | 4.5  | Ю      |  |

| Through and Cata Charres (1)    | Og/th)  | Vds = 12.5 V, Ids = 8 A  | Q1 |      | 0.30 |      |        |  |

| Threshold Gate Charge (1)       | Qg(th)  | Vds = 12.5 V, Ids = 13 A | Q2 |      | 0.76 |      | nC     |  |

| Cata Sauraa Charga              | Ogo     | Vds = 12.5 V, Ids = 8 A  | Q1 |      | 0.56 |      | 2      |  |

| Gate-Source Charge              | Qgs     | Vds = 12.5 V, Ids = 13 A | Q2 |      | 0.86 |      | nC     |  |

| Cata Drain (Miller) Charge      | Oad     | Vds = 12.5 V, Ids = 8 A  | Q1 |      | 0.16 |      | °C     |  |

| Gate-Drain (Miller) Charge      | Qgd -   | Vds = 12.5 V, Ids = 13 A | Q2 |      | 0.33 | nC   |        |  |

| Output Charge                   | 0000    | Vds = 12.5 V, Ids = 8 A  | Q1 |      | 3.1  |      | »C     |  |

| Output Charge                   | Qoss    | Vds = 12.5 V, Ids = 13 A | Q2 |      | 7.5  |      | nC     |  |

<sup>1)</sup> Qg(th) is defined as the gate charge value to the measured value of the gate-source threshold voltage, Vgs(th).

# **Product Ordering Information**

SZPB9317A-BF34 15 V, 8 Amp Half Bridge in a 3.7mm x 4 mm, 0.5 mm lead pitch, 18 lead QFN package.

# **Product Image**

Figure 3: SZPB9317A-B Product Image

SZPB9317A-B **DATASHEET**

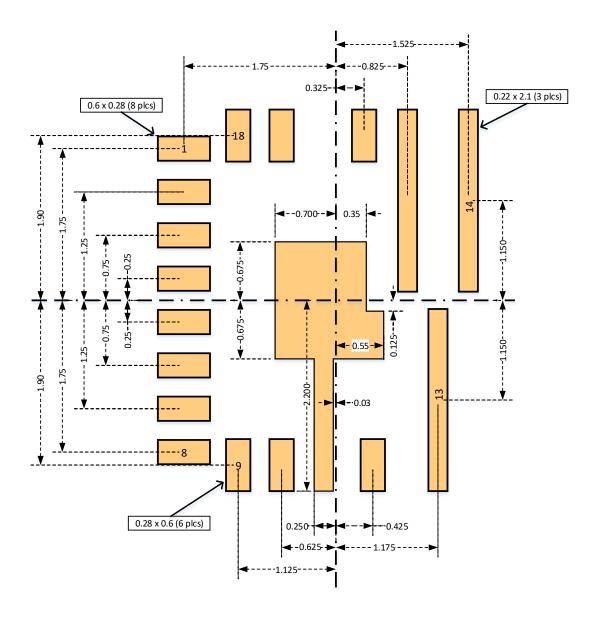

# **Package Dimensions**

|        | DIMENSIC | N TABLE   |         |  |  |

|--------|----------|-----------|---------|--|--|

| SYMBOL | MINIMUM  | NOMINAL   | MAXIMUM |  |  |

| Α      | 0.80     | 0.90      | 1.00    |  |  |

| A1     | 0.00     | 0.02      | 0.05    |  |  |

| A3     |          | 0.203 Ref |         |  |  |

| Ь1     | 0.18     | 0.23      | 0.28    |  |  |

| b2     | 0.15     | 0.20      | 0.25    |  |  |

| Ь3     | 0.25     | 0.30      | 0.35    |  |  |

| D      |          | 3.70 BSC  |         |  |  |

| E      |          | 4.00 BSC  |         |  |  |

| D1     | 1.00     | 1.10      | 1.20    |  |  |

| D2     | 1.20     | 1.30      | 1.40    |  |  |

| E1     | 1.22     | 1.32      | 1.42    |  |  |

| e1     |          | 0.50 BSC  |         |  |  |

| e2     |          | 0.95 BSC  |         |  |  |

| e3     |          | 0.70 BSC  |         |  |  |

| e4     | 0.55 BSC |           |         |  |  |

| L1     | 0.25     | 0.35      | 0.45    |  |  |

| L2     | 1.77     | 1.87      | 1.97    |  |  |

| N      |          | 18        |         |  |  |

- NOTE:

1. Dimensioning and tolerancing conform to ASME Y14.5—2009

2. All dimensions are in millimeters

3. N is the total number of terminals

4. Unilateral coplanarity zone applies to the exposed pas as well as the

Figure 4: F34 Package Dimensions

# **Recommended PCB Footprint**

**Figure 5: Recommended PCB Footprint**

SZPB9317A-B **DATASHEET**

# **Revision History**

| Date            | Revision | Notes                                       | Author |

|-----------------|----------|---------------------------------------------|--------|

| June 18, 2018   | 1.0      | Initial release                             | TW     |

| August 21, 2018 | 2.0      | Adjusted Thermal Information specs.         | TW     |

| March 12, 2019  | 3.0      | Final Datasheet release.                    | TW     |

| June 20, 2019   | 4.0      | Update header/footers and add the new logo. | CR     |

Silanna Semiconductor Proprietary and Confidential

Information furnished by Silanna Semiconductor is believed to be accurate and reliable. However, no responsibility is assumed for its use. Silanna Semiconductor makes no representation that the interconnection of its circuits as described herein will not infringe on existing patents rights.

> 4795 Eastgate Mall, Suite 100, San Diego, CA 92121 Toll Free: (888) 637-3564 | Fax: (858) 373-0437 | www.powerdensity.com